ФкДцИКд№Яђ CPU ЬсЙЉдЫЫуЫљашЕФдЪМЪ§ОнЃЌЖјФПЧА CPU дЫааЫйЖШГЌЙ§ФкДцЪ§ОнДЋЪфЫйЖШКмЖрЁЃвђДЫЃЌКмЖрЧщПіЯТЃЌCPU ЖМашвЊЕШД§ФкДцЬсЙЉЪ§ОнЃЌетОЭЪЧГЃЫЕЕФ“CPU ЕШД§ЪБМф”ЁЃФкДцДЋЪфЫйЖШдНТ§ЃЌCPU ЕШД§ЪБМфОЭЛсдНГЄЃЌЯЕЭГећЬхадФмЪмЕНЕФгАЯьОЭдНДѓЁЃвђДЫЃЌПьЫйЕФФкДцЃЌЪЧгааЇЬсЩ§ CPU аЇТЪКЭећЛњадФмЕФЙиМќжЎвЛЁЃ

ЁЁЁЁдкЪЕМЪЙЄзїЪБЃЌЮоТлЪВУДРраЭЕФФкДцЃЌдкЪ§ОнБЛДЋЪфжЎЧАЃЌДЋЫЭЗНБиаыЛЈЗбвЛЖЈЪБМфШЅЕШД§ДЋЪфЧыЧѓЕФЯьгІЃЌЭЈЫзЕуЫЕЃЌОЭЪЧДЋЪфЧАЃЌДЋЪфЫЋЗНБиаывЊНјааБивЊЕФЭЈаХЃЌЖјетбљОЭЛсдьГЩДЋЪфЕФвЛЖЈбгГйЪБМфЁЃCL ЩшжУвЛЖЈГЬЖШЩЯЗДгГГіСЫИУФкДцдк CPU НгЕНЖСШЁФкДцЪ§ОнЕФжИСюКѓЃЌЕНе§ЪНПЊЪМЖСШЁЪ§ОнЫљашЕФЕШД§ЪБМфЁЃВЛФбПДГіЃЌЭЌЦЕТЪЕФФкДцЃЌCL ЩшжУЕЭЕФЃЌИќОпгаЫйЖШгХЪЦЁЃ

ЁЁЁЁЩЯУцжЛЪЧИјДѓМвНЈСЂвЛИіЛљБОЕФ CL ИХФюЁЃЖјЪЕМЪЩЯЃЌФкДцбгГйЕФЛљБОвђЫиЃЌОјЖдВЛжЙетаЉЁЃФкДцбгГйЪБМфЃЌгаИізЈУХЕФЪѕгяНа“Latency”ЁЃвЊаЮЯѓЕФСЫНтбгГйЃЌЮвУЧВЛЗСАбФкДцЕБГЩвЛИіДцДЂзХЪ§ОнЕФЪ§зщЃЌЛђепвЛИі EXCEL БэИёЃЌвЊШЗЖЈУПИіЪ§ОнЕФЮЛжУЃЌУПИіЪ§ОнЖМЪЧвдааКЭСаБрХХађКХРДБъЪОЃЌдкШЗЖЈСЫааЁЂСаађКХжЎКѓЃЌИУЪ§ОнОЭЮЈвЛСЫЁЃФкДцЙЄзїЪБЃЌдквЊЖСШЁЛђаДШыФГЪ§ОнЃЌФкДцПижЦаОЦЌЛсЯШАбЪ§ОнЕФСаЕижЗДЋЫЭЙ§ШЅЃЌетИі RAS аХКХЃЈRow Address StrobeЃЌааЕижЗаХКХЃЉОЭБЛМЄЛюЃЌЖјдкзЊЛЏЕНааЪ§ОнЧАЃЌашвЊОЙ§МИИіжДаажмЦкЃЌШЛКѓНгЯТРД CAS аХКХЃЈColumn Address StrobeЃЌСаЕижЗаХКХЃЉБЛМЄЛюЁЃдк RAS аХКХКЭ CAS аХКХжЎМфЕФМИИіжДаажмЦкЃЌОЭЪЧ RAS-to-CAS бгГйЪБМфЁЃдк CAS аХКХБЛжДаажЎКѓЃЌЭЌбљвВашвЊМИИіжДаажмЦкЁЃДЫжДаажмЦкдкЪЙгУБъзМ PC133 ЕФ SDRAM ДѓдМЪЧ 2ЈD3 ИіжмЦкЃЛЖј DDR RAM дђЪЧ 4ЈD5 ИіжмЦкЁЃдк DDR жаЃЌеце§ЕФ CAS бгГйЪБМфдђЪЧ 2ЈD2.5 ИіжДаажмЦкЁЃRAS-to-CAS ЕФЪБМфЃЌдђЪгММЪѕЖјЖЈЃЌДѓдМЪЧ 5ЈD7 ИіжмЦкЃЌетвВЪЧбгГйЕФЛљБОвђЫиЁЃ

ЁЁЁЁCL ЩшжУНЯЕЭЕФФкДцЃЌОпБИИќИпЕФгХЪЦЃЌетПЩвдДгзмЕФбгГйЪБМфРДБэЯжЁЃФкДцзмЕФбгГйЪБМфгавЛИіМЦЫуЙЋЪНЃЌзмбгГйЪБМфЃНЯЕЭГЪБжгжмЦк×CLФЃЪНЪ§ЃЋДцШЁЪБМфЃЈtACЃЉЁЃЪзЯШЃЌРДСЫНтвЛЯТДцШЁЪБМфЃЈtACЃЉЕФИХФюЁЃtAC ЪЧ Access Time from CLK ЕФЫѕаДЃЌЪЧжИзюДѓ CAS бгГйЪБЕФзюДѓЪ§ЪфШыЪБжгЃЌЪЧвдФЩУыЮЊЕЅЮЛЕФЃЌгыФкДцЪБжгжмЦкЪЧЭъШЋВЛЭЌЕФИХФюЃЌЫфШЛЖМЪЧвдФЩУыЮЊЕЅЮЛЁЃДцШЁЪБМфЃЈtACЃЉДњБэзХЖСШЁЁЂаДШыЕФЪБМфЃЌЖјЪБжгЦЕТЪдђДњБэФкДцЕФЫйЖШЁЃ

ЁЁЁЁОйИіР§згЃЌРДМЦЫувЛЯТзмбгГйЪБМфЁЃБШШчЃЌвЛЬѕ DDR333 ФкДцЃЌЦфДцШЁЪБМфЮЊ 6nsЃЌЦфФкДцЪБжгжмЦкЮЊ 6nsЃЈDDRФкДцЪБжгжмЦкЃН1X2/ФкДцЦЕТЪЃЌDDR333 ФкДцЦЕТЪЮЊ 333ЃЌдђПЩМЦЫуГіЦфЪБжгжмЦкЮЊ 6nsЃЉЁЃЮвУЧдкжїАхЕФ BIOS жаЃЌНЋЦф CL ЩшжУЮЊ 2.5ЃЌдђзмЕФбгГйЪБМфЃН6ns X2.5ЃЋ6nsЃН21nsЁЃЖјШчЙћ CL ЩшжУЮЊ 2ЃЌФЧУДзмЕФбгГйЪБМфЃН6ns X2ЃЋ6nsЃН18nsЃЌОЭМѕЩйСЫ 3ns ЕФЪБМфЁЃ

ЁЁЁЁДгзмЕФбгГйЪБМфРДПДЃЌCL жЕЕФДѓаЁЦ№ЕНСЫКмЙиМќЕФзїгУЁЃЫљвдЃЌЖдЯЕЭГвЊЧѓИпКЭЯВЛЖГЌЦЕЕФгУЛЇЃЌЭЈГЃЯВЛЖЙКТђ CL жЕНЯЕЭЕФФкДцЁЃФПЧАЃЌИїФкДцПХСЃГЇЩЬГ§СЫДгЬсИпФкДцЪБжгЦЕТЪРДЬсИп DDR ЕФадФмжЎЭтЃЌвбОПМТЧЭЈЙ§ИќНјвЛВНЕФНЕЕЭ CAS бгГйЪБМфЃЌРДЬсИпФкДцадФмЁЃВЛЭЌРраЭФкДцЕФЕфаЭ CL жЕВЂВЛЯрЭЌЁЃР§ШчЃЌФПЧАЕфаЭ DDR ЕФ CL жЕЮЊ 2.5 Лђеп 2ЃЌЖјДѓВПЗж DDR2 533 ЕФбгГйВЮЪ§ЖМЪЧ 4 Лђеп 5ЃЌЩйСПИпЖЫ DDR2 ЕФ CL жЕПЩвдДяЕН 3ЁЃ

ЁЁЁЁВЛЙ§ЃЌВЂВЛЪЧЫЕ CL жЕдНЕЭадФмОЭдНКУЃЌвђЮЊЦфЫќЕФвђЫиЛсгАЯьетИіЪ§ОнЁЃР§ШчЃЌаТвЛДњДІРэЦїЕФИпЫйЛКДцНЯгааЇТЪЃЌетБэЪОДІРэЦїБШНЯЩйЕижБНгДгФкДцЖСШЁЪ§ОнЁЃдйепЃЌСаЕФЪ§ОнЛсБШНЯГЃБЛДцШЁЃЌЫљвд RAS-to-CAS ЕФЗЂЩњМИТЪвВДѓЃЌЖСШЁЕФЪБМфвВЛсдіЖрЁЃзюКѓЃЌгаЪБЛсЗЂЩњЭЌЪБЖСШЁДѓСПЪ§ОнЕФЧщаЮЃЌдкетжжЧщаЮЯТЃЌЯрСкЕФФкДцЪ§ОнЛсвЛДЮБЛЖСШЁГіРДЃЌCAS бгГйЪБМфжЛЛсЗЂЩњвЛДЮЁЃ

ЁЁЁЁбЁдёЙКТђФкДцЪБЃЌзюКУбЁдёЭЌбљ CL ЩшжУЕФФкДцЁЃвђЮЊВЛЭЌЫйЖШЕФФкДцЃЌЛьВхдкЯЕЭГФкЃЌЯЕЭГЛсвдНЯТ§ЕФЫйЖШРДдЫааЃЌвВОЭЪЧЕБ CL 2.5 КЭ CL 2 ЕФФкДцЭЌЪБВхдкжїЛњФкЃЌЯЕЭГЛсздЖЏШУСНЬѕФкДцЖМЙЄзїдк CL 2.5 зДЬЌЃЌдьГЩзЪдДРЫЗбЁЃ

ФкДцжЊЪЖЯъНт-CLЩшжУ

ЗЂВМЪБМфЃК2013-07-04 РДдДЃКВЉДѓЕчФдЭј

еЊвЊ:ФкДцжЊЪЖЯъНт-CLЩшжУ

ЯрЙидФЖСЃК

ЭМЮФЭЦМі

ЭЦМідФЖС

- ЁЄШчКЮбЁЙКБЪМЧБОФкДцЬѕ

- ЁЄБЪМЧБОЕчФдЕФЯЕЭГЬсЪОФкДцВЛзу

- ЁЄIBMБЪМЧБОФкДцЖЬТЗЕМжТЮоЗЈМгЕч

- ЁЄЕчФдФкДцгыащФтФкДц МЦЫуЛњЕФФкДцЙмРэФмСІ

- ЁЄЗжЮіащФтФкДцОЕфЩшжУЮѓЧјЕФНтОіЗНЗЈУшЪі

- ЁЄЕчФдЙЪеЯЫйХХЗНЗЈжЎФкДцЦЊ ЫцЛњадЫРЛњ

- ЁЄWin XPжаЕЅЛїгвМќеМДѓСПФкДц

- ЁЄДђгЁЛњЃКзюДѓФкДц

- ЁЄФкДцЕФжжРрМАЦфЪЙгУЧГЬИ

- ЁЄШчКЮевЛиЖЊЪЇЕФФкДцЬѕ

ЦфЫћШЫе§дкПДЁЁ

- ЁЄащЫЦФкДцЪЧЩЖЃПащЫЦЖрДѓВХКУЃПащЫЦФкДцШчКЮЩшжУ

- ЁЄФкДцЪЧВЛЪЧдНДѓдНКУ

- ЁЄФкДцЫќЪЧдѕУДЙЄзїЕФФиЃПФкДцЙЄзїдРэ

- ЁЄФкДцЕФЙЪеЯЦЪЮі ИјДѓМвЗжЮіМИИіЕфаЭЕФФкДцЙЪеЯ

- ЁЄзЂВсБэЦЕЦЕГіДэЛіЦ№ФкДц

- ЁЄзщНЈЁАЫЋЭЈЕРФкДцЁБгХШБЕу

- ЁЄБЪМЧБОЕчФдФкДцАВзАЗНЗЈНщЩм

- ЁЄзпГіащФтЕФФкДцНћгУЮѓЧј

- ЁЄДїЖћБЪМЧБОФкДцЙЪеЯЮЌаоЪЕР§

- ЁЄПЊЛњЬсЪОФкДцДэЮѓИУШчКЮНтОі

- ЁЄгХЛЏWindows XPЯЕЭГФкДцЗНЗЈ

- ЁЄБЪМЧБОЕчФддѕбљЩ§МЖФкДцзюБЃЯе

- ЁЄWindowsЯЕЭГащФтФкДцГЃгіЮЪЬт

- ЁЄДђгЁФкДцВЛзуОПОЙЮЊФФАу МАЪБЧхГ§ЯЕЭГВЁЖО

- ЁЄФкДцвьГЃЙЪеЯХХГ§ЗНЗЈ

- ЁЄФкДцв§Ц№ЫцЛњадЫРЛњЙЪеЯЕФЗжЮігыДІРэ

- ЁЄФкДцЙЪеЯеяЖЯ ПЩвдАДееЮхИіВНжшНјааеяЖЯХХГ§

- ЁЄVISTAЯТШчКЮВщПДФкДцШнСП

- ЁЄФкДцШчКЮГЌЦЕФиЃП

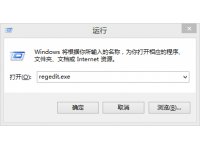

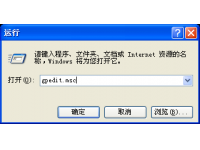

- ЁЄФкДцжЊЪЖЯъНт-CLЩшжУ